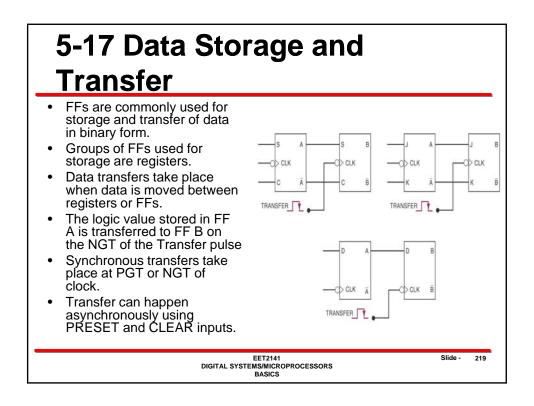

## 5-17 Data Storage and **Transfer** Asynchronous transfers are controlled by PRE and CLR inputs. When Transfer Enable is low, the two NAND gate are HIGH (Asynchronous inputs are inactive) When the Transfer Enable is HIGH, depends on the state of A, the FF either is SET or Cleared. PRE в > CLK CLK CLR B Transfe 220 EET2141 Slide -DIGITAL SYSTEMS/MICROPROCESSORS BASICS